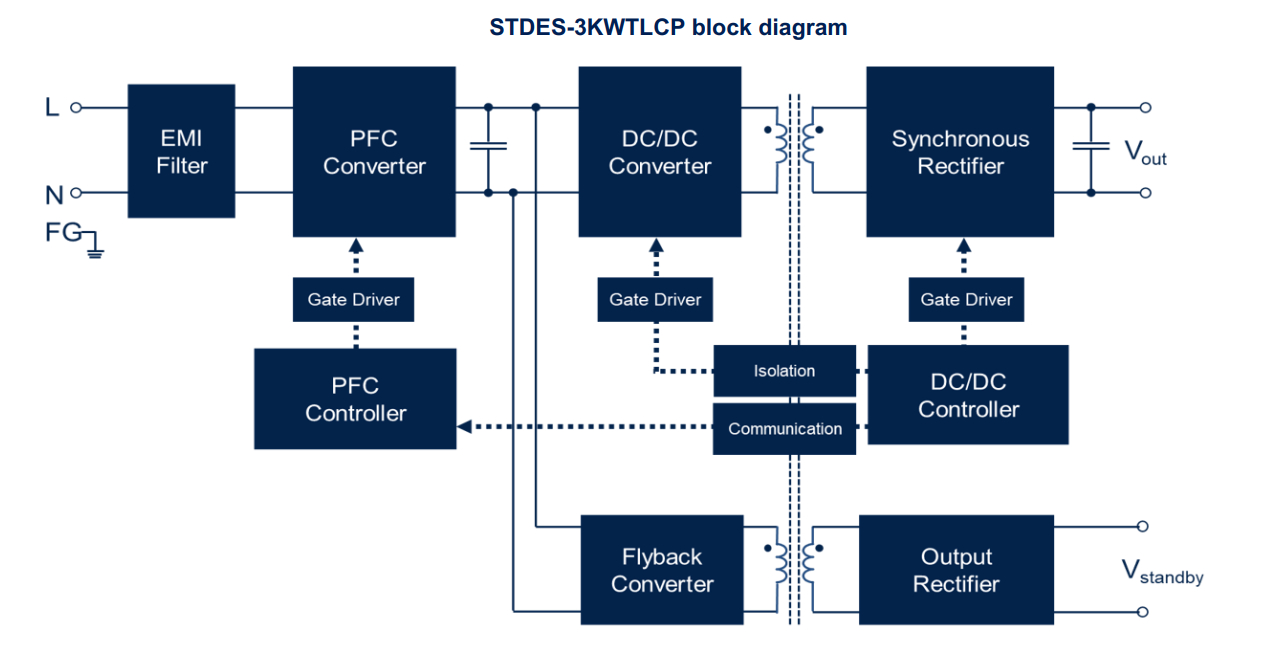

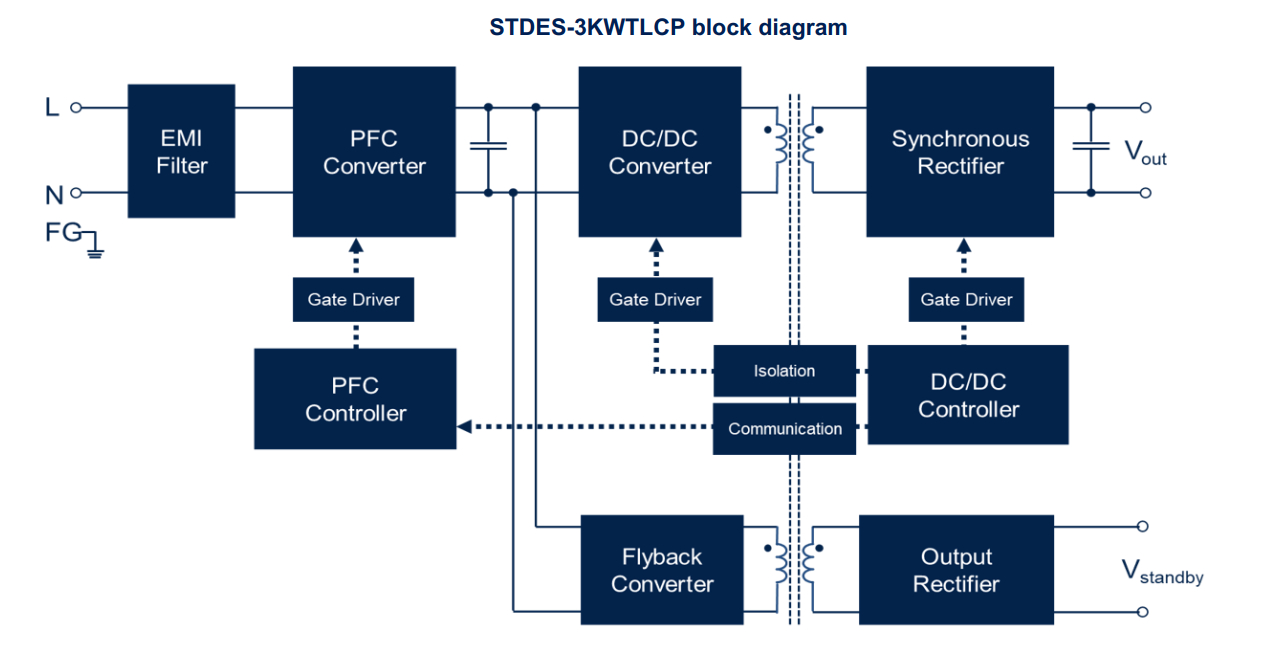

STDES-3KWTLCP參考設計針對5G通信應用的3 kW/53.5V AC-DC轉換器電源,使用完整的ST數字電源解決方案。

電路設計包括前端無橋圖騰柱PFC和後端LLC全橋架構。前級圖騰柱PFC提供功率因數校正(PFC)和諧波失真(THD)抑制,後記全橋LLC轉換器提供安全隔離和穩定的輸出電壓。

該參考設計為高效率緊湊型解決方案,在230 VAC輸入時,測量峰值效率為96.3%,低THD失真(滿載時小於5%THD)並減少了材料成本。

外形尺寸為105 mm x 281 mm x 41 mm,功率密度高達40 W/in³。

該電源由兩個功率級組成:一個由STM32G474RBT6 MCU 控制的無橋圖騰極PFC, 以及次級 由另一個 STM32G474RBT6 MCU 控制的全橋LLC+同步整流(SR)。

STDES-3KWTLCP還可以幫助用戶使用ST最新的功率器件:第三代半導體SIC MOSFET、高壓MDmesh MOSFET、超結MOSFET、隔離MOS 驅動器和VIPer系列輔助電源。

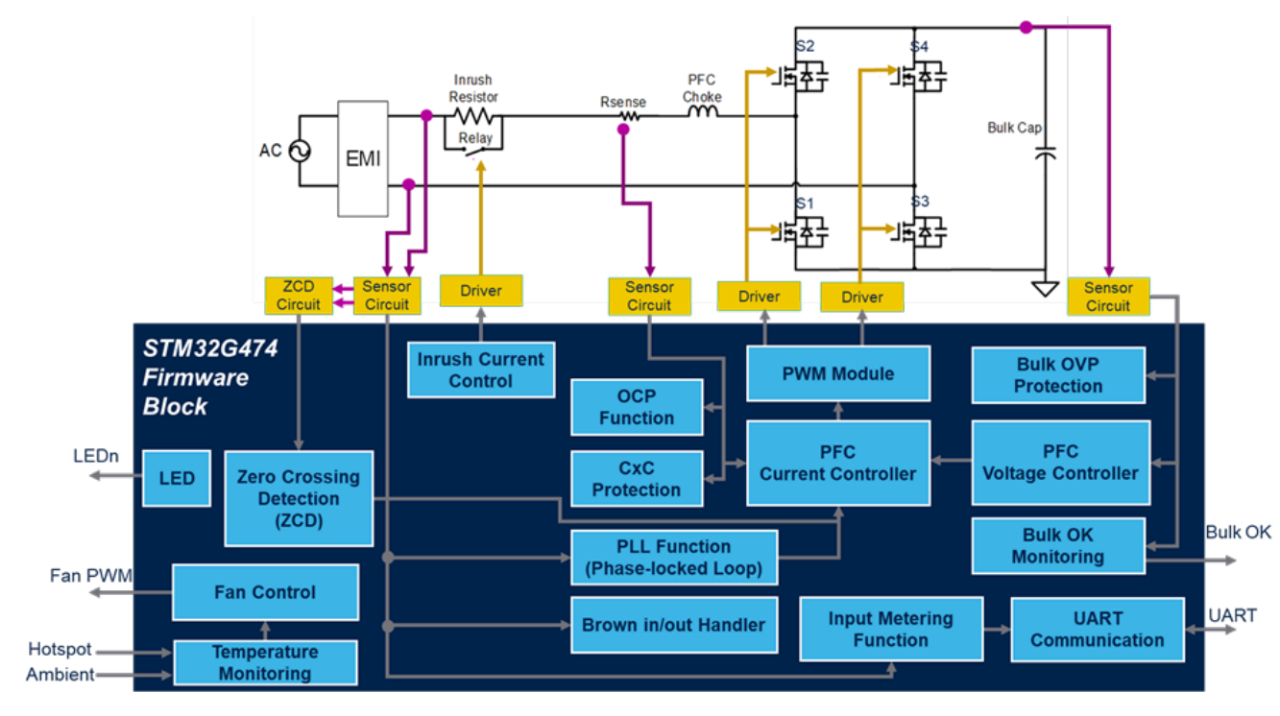

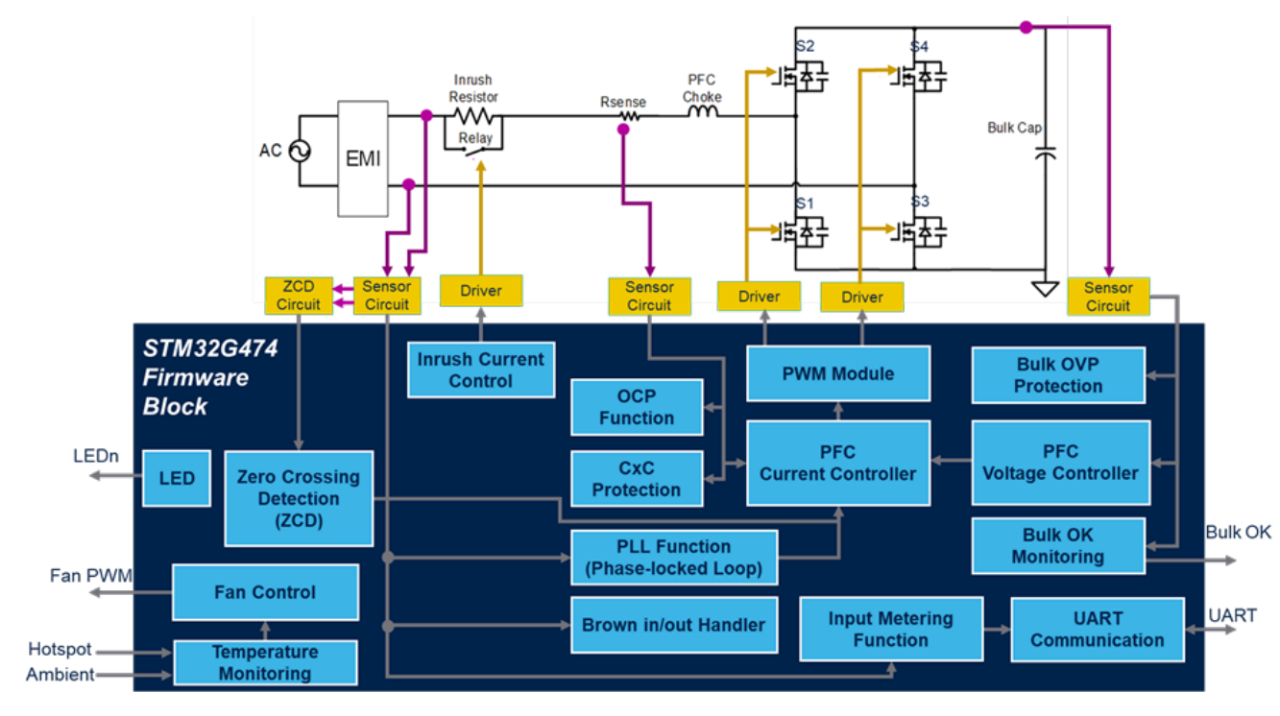

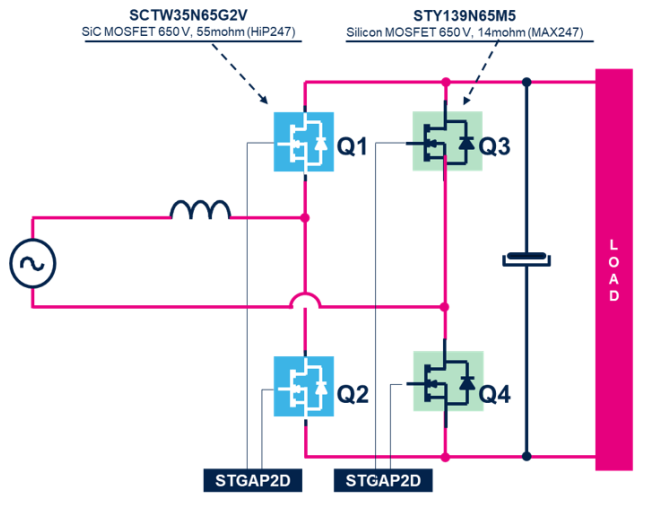

使用STM32G474RBT6 MCU 控制的前級無橋圖騰柱PFC 實現原理如下圖:

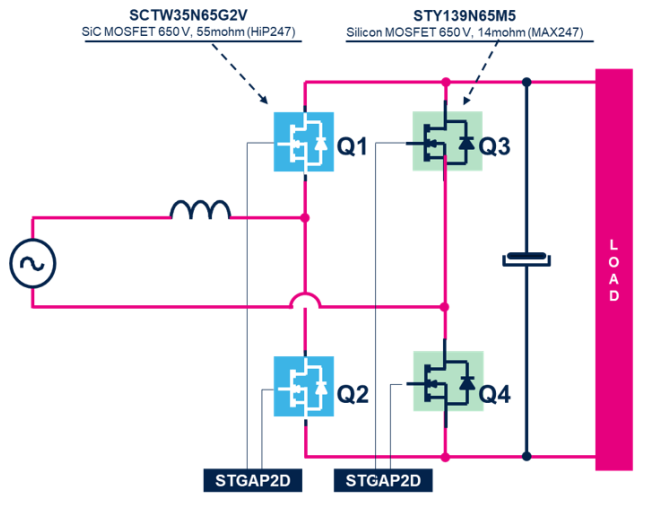

圖騰柱PFC的架構模型如下圖,四顆MOS在MCU的控制下,交替導通,實現功率因數校正的目的,其中左側兩顆,必須使用第三代寬禁帶半導體,如SIC,GNA,本案例中使用的是ST第二代SIC SCTW35N65G2V。

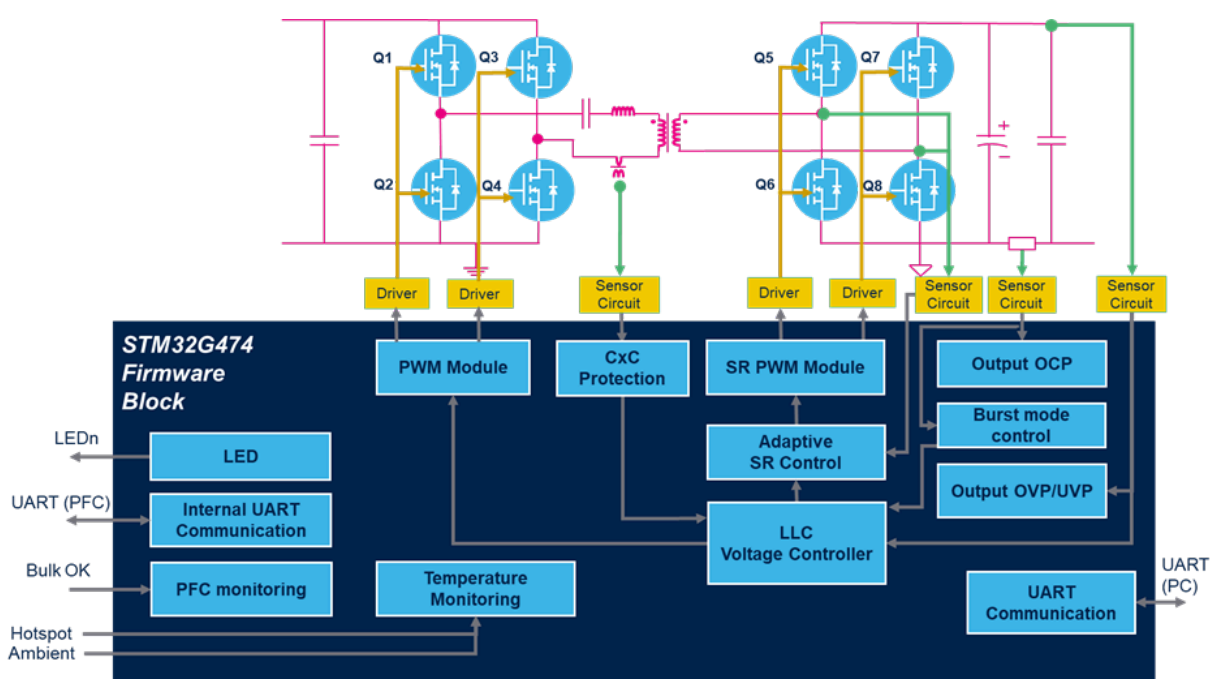

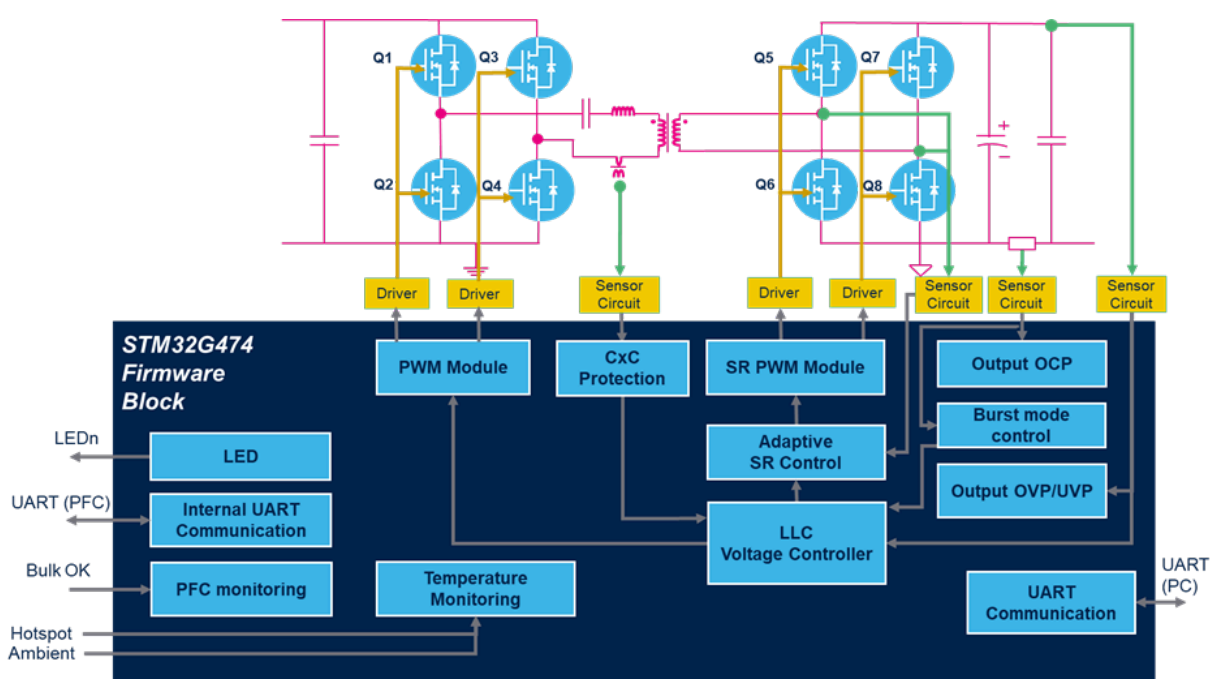

使用STM32G474RBT6 MCU 控制的LLC + SR 實現原理如下圖:

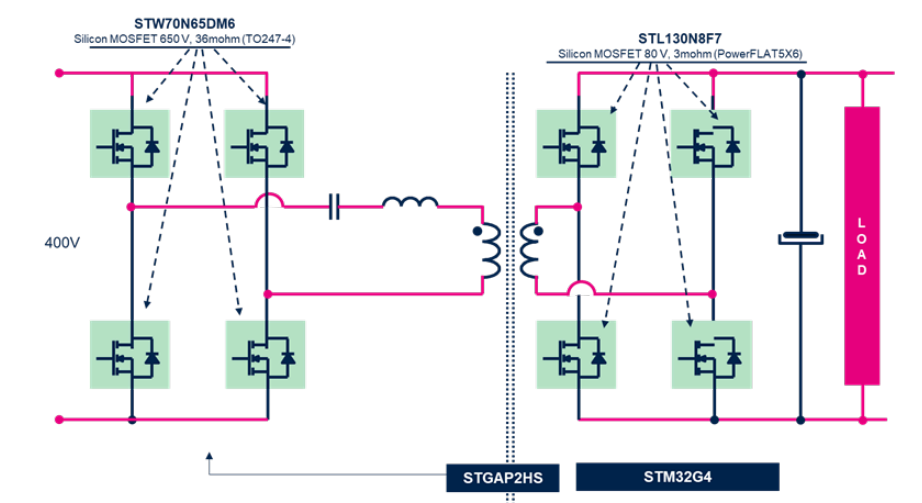

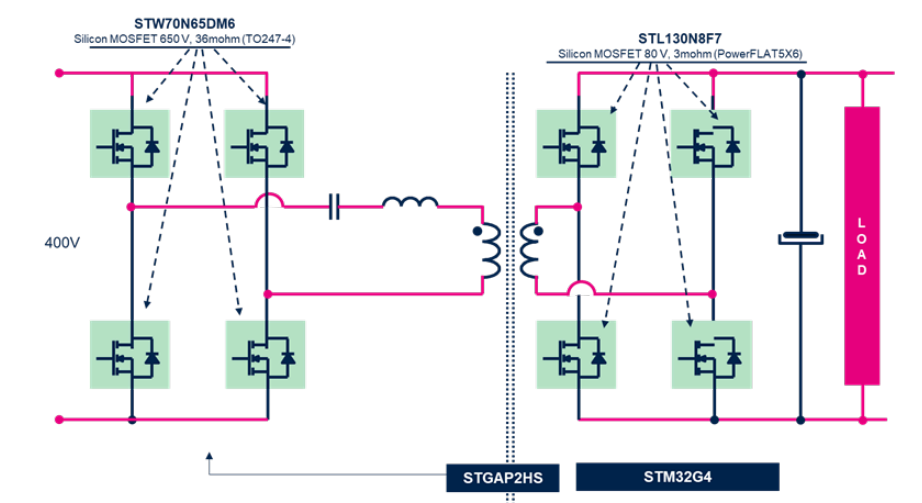

全橋LLC 的架構模型如下圖,初級側四顆高壓MOS 使用ST低損耗的M6系列超結MOSFET ---STW70N65DM6 ,次級側四顆低壓MOS使用 STL130N8F7, SMD 5*6mm封裝,導通阻抗3mR.

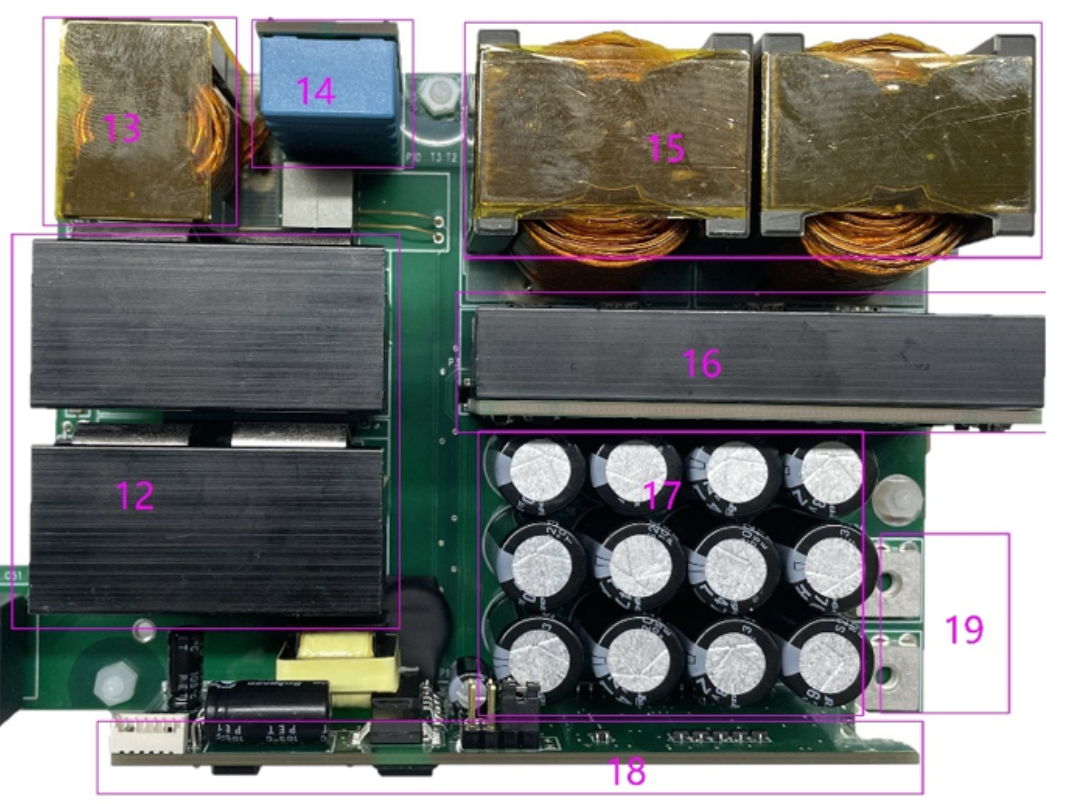

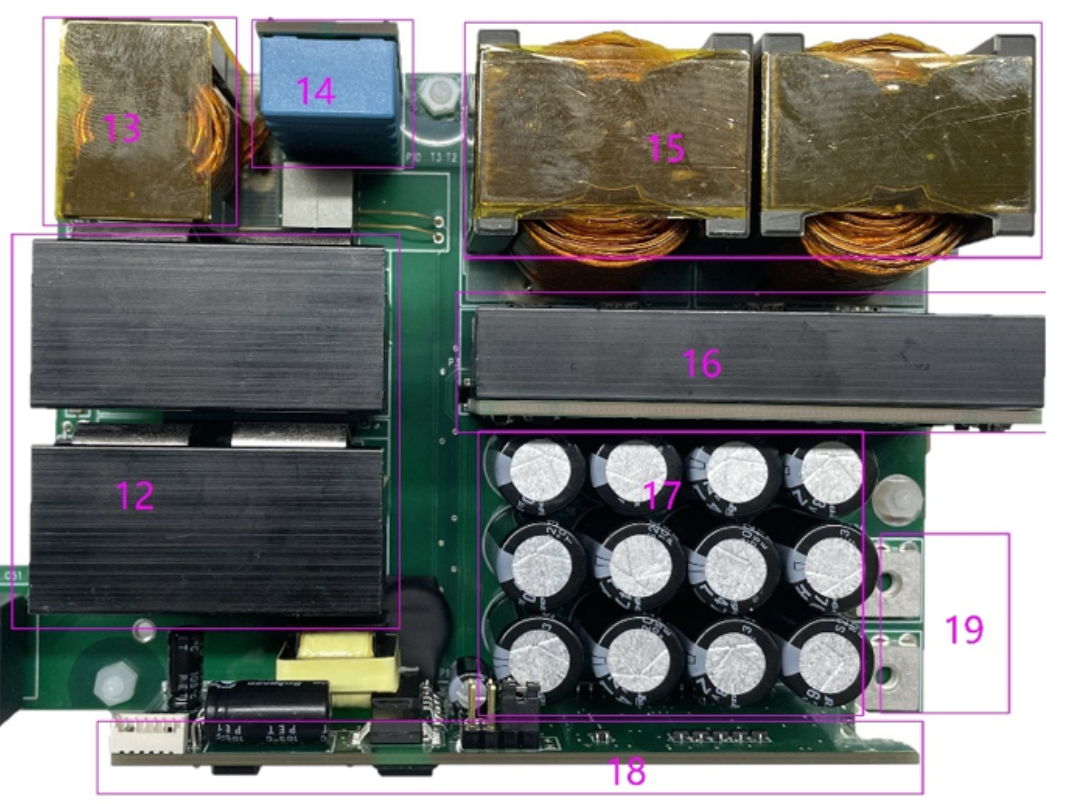

後級LLC轉換部分,各主要功率器件的分布如下,結構非常緊湊:

12--高壓MOS STW70N65DM6

13--諧振電感

14--諧振電容

15--主變壓器

16--次級同步整流低壓MOS

17--輸出電容

18--MCU控制小板

電路設計包括前端無橋圖騰柱PFC和後端LLC全橋架構。前級圖騰柱PFC提供功率因數校正(PFC)和諧波失真(THD)抑制,後記全橋LLC轉換器提供安全隔離和穩定的輸出電壓。

該參考設計為高效率緊湊型解決方案,在230 VAC輸入時,測量峰值效率為96.3%,低THD失真(滿載時小於5%THD)並減少了材料成本。

外形尺寸為105 mm x 281 mm x 41 mm,功率密度高達40 W/in³。

該電源由兩個功率級組成:一個由STM32G474RBT6 MCU 控制的無橋圖騰極PFC, 以及次級 由另一個 STM32G474RBT6 MCU 控制的全橋LLC+同步整流(SR)。

STDES-3KWTLCP還可以幫助用戶使用ST最新的功率器件:第三代半導體SIC MOSFET、高壓MDmesh MOSFET、超結MOSFET、隔離MOS 驅動器和VIPer系列輔助電源。

使用STM32G474RBT6 MCU 控制的前級無橋圖騰柱PFC 實現原理如下圖:

圖騰柱PFC的架構模型如下圖,四顆MOS在MCU的控制下,交替導通,實現功率因數校正的目的,其中左側兩顆,必須使用第三代寬禁帶半導體,如SIC,GNA,本案例中使用的是ST第二代SIC SCTW35N65G2V。

使用STM32G474RBT6 MCU 控制的LLC + SR 實現原理如下圖:

全橋LLC 的架構模型如下圖,初級側四顆高壓MOS 使用ST低損耗的M6系列超結MOSFET ---STW70N65DM6 ,次級側四顆低壓MOS使用 STL130N8F7, SMD 5*6mm封裝,導通阻抗3mR.

後級LLC轉換部分,各主要功率器件的分布如下,結構非常緊湊:

12--高壓MOS STW70N65DM6

13--諧振電感

14--諧振電容

15--主變壓器

16--次級同步整流低壓MOS

17--輸出電容

18--MCU控制小板

►場景應用圖

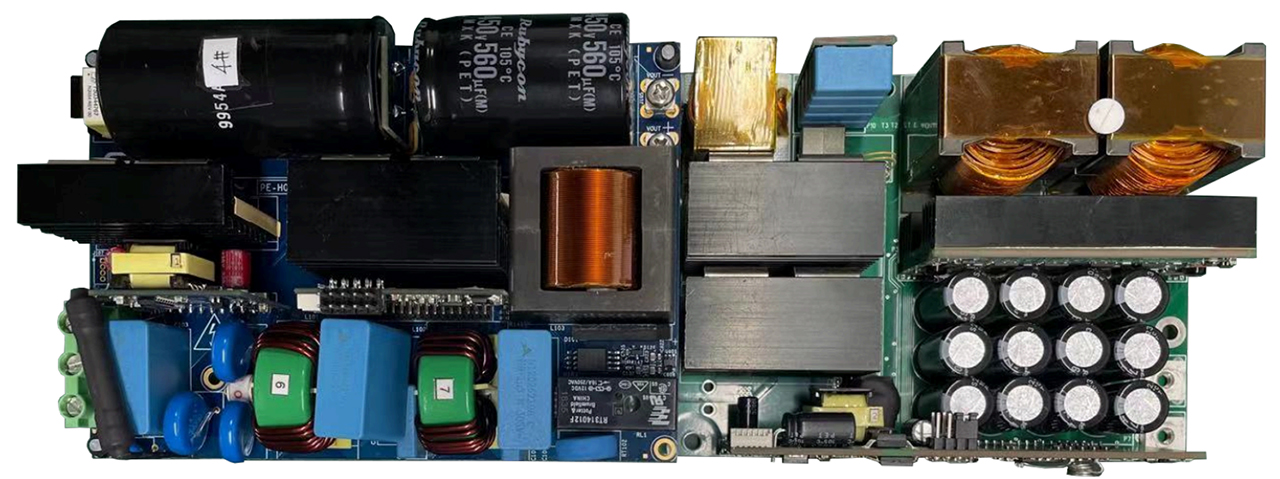

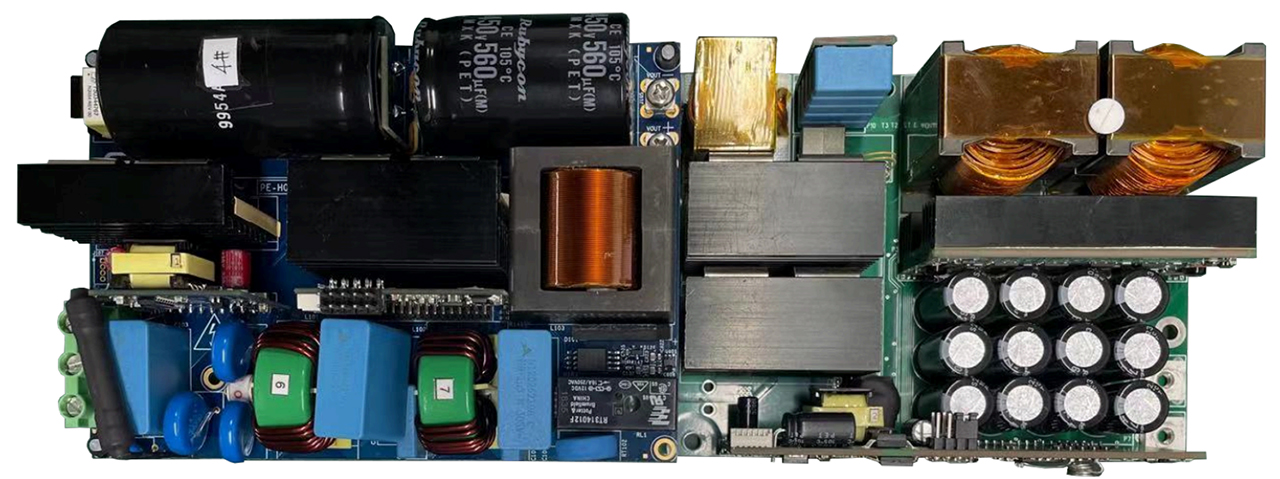

►展示板照片

►方案方塊圖

►核心技術優勢

•採用ST SIC MOS(寬禁帶第三代半導體), 高溫低阻,低開關損耗,低體二極體反向恢復電荷。 •主控MCU晶片ST32M474,全數字設計電源控制。 •功率密度達: 40 W/in^3。 •滿負載時高功率因數&總諧波失真 THD <5% 。 •峰值浪涌電流<30A 。

►方案規格

•輸入電壓:90~264V •輸入電壓頻率:47~63HZ •輸出電壓:53.5V •輸出功率:3000W •功率因數>0.98 @滿負載 •峰值效率 96.3%