-

本方案採用FPGA作為驅動屏幕的裝置,有下列幾項優點:

- 適合各種不同TFT-LCD的介面規格,諸如 並口 RGB 888/ BT656/ BT709 /LVDS /MIPI DSI 等市場規格上常用的介面

- 支持不同分辨率的屏,可以從320x240 ,640x480 , 800x600 , 1280x720, 1024x 800, 1920x1080 ,640x480 , 800x600 , 1280x720, 1024x 800, 1920x1080 等

- 支持不同禎率的要求,如 30禎/60/60禎 等等

- 支持字褲與圖形編碼,在許多應用中,可以自由定義英數字及中文繁體簡體和特殊符號等,可以顯示在屏幕上,並給予不同顏色與底圖的算法,當需要文字與底圖疊加的功能要求也能輕易做到

- 方案簡單,由於採用邏輯編碼,不容易死機,,不會像MCU一樣容易跑飛而當機或花屏

- 升級容易,只要在FPGA的邏輯容量範圍內,可以隨意改變邏輯編排,方便增加功能與提升性能,不需要額外的電路輔助

-

簡單易用的邏輯編成軟體綜合佈局佈線工具,以下將以簡單的步驟與方法帶領各位入門

- 下列介紹如何編寫RTL代碼點亮TFT LCD顯示屏幕

- 材料:

- FPGA Lattice FPGA XO2

- TFT LCD 800X480

- USB 下載線

- Verilog 編譯工具

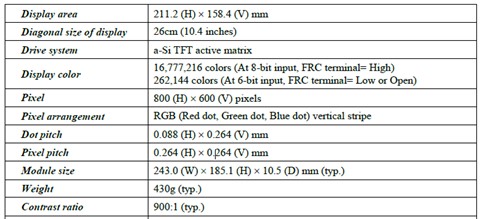

- TFT LCD 屏幕介紹:

- 先選用適合分辨率的屏:

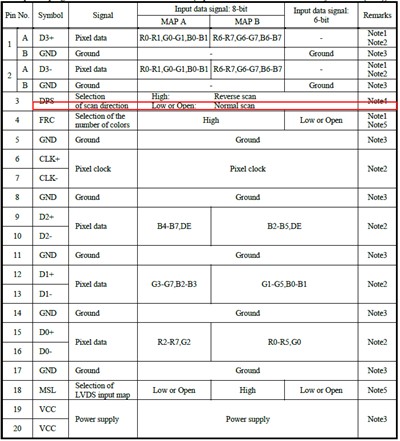

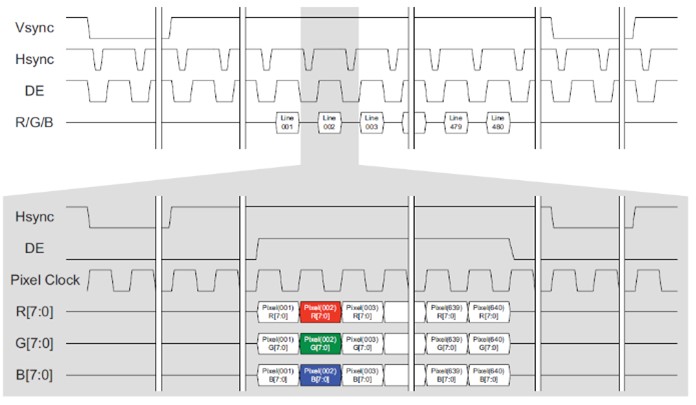

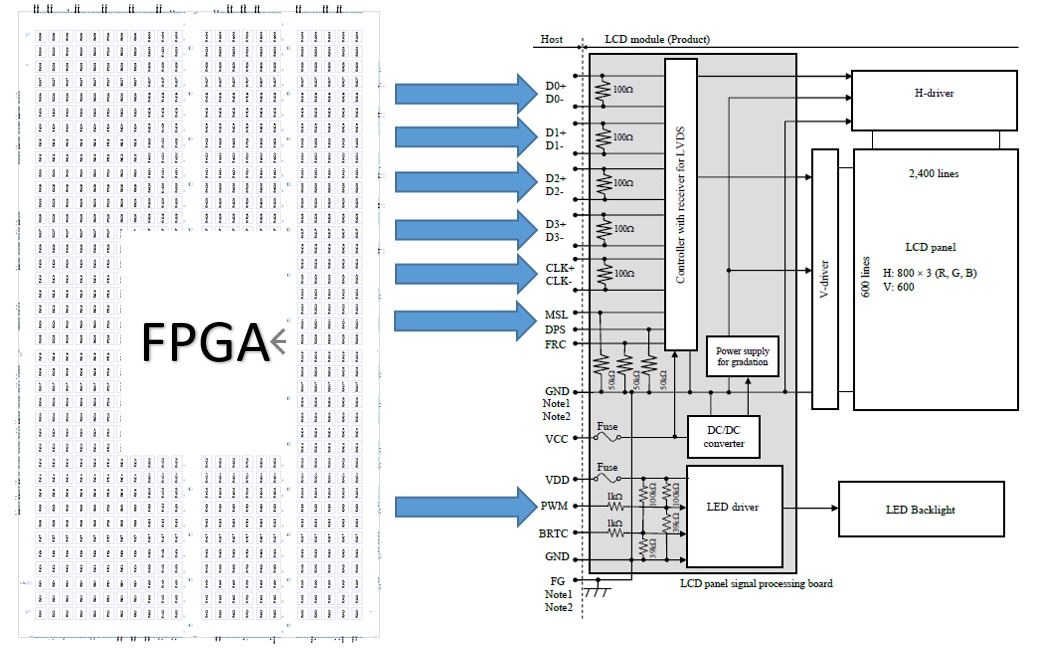

- 下方所示的屏幕規格為: 800 X 600 點RGB 格式

- 色彩深度為 16,777,216色深(24bit) 或 262,144色深(18 bit)

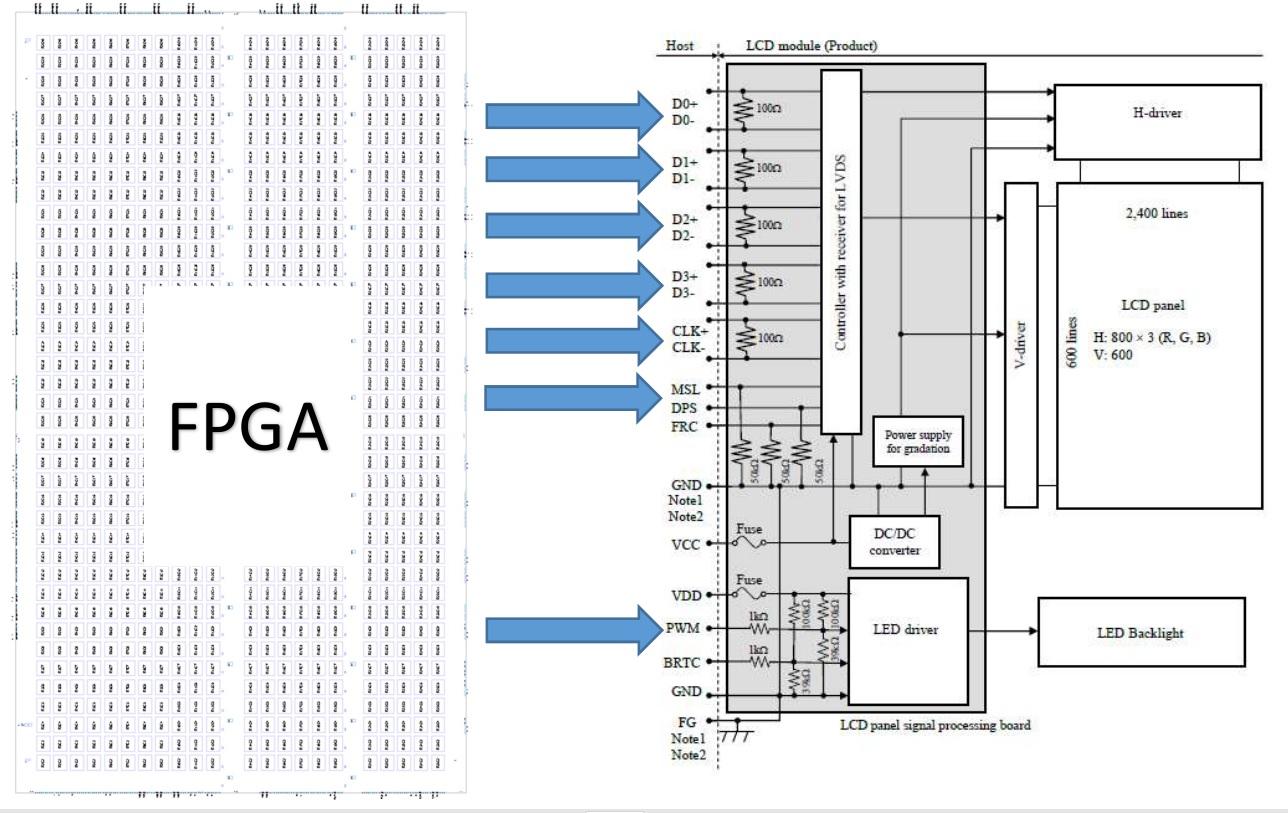

- 連接線的接法:LVDS腳位說明:

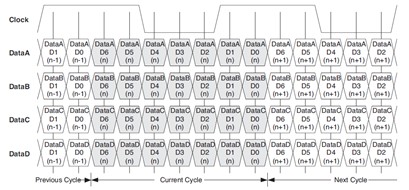

- 把FPGA LVDS Pin 接到TFT LCD LVDS Pin(D0+/D0-/ D1+/D1-/ D2+/D2-/ D3+/D3-/CLK+/CLK-)

- 先選用適合分辨率的屏:

- ideo 的LVDS內容說明:

- 把FPGA I/O Pin 接到TFT LCD LED PWM Pin

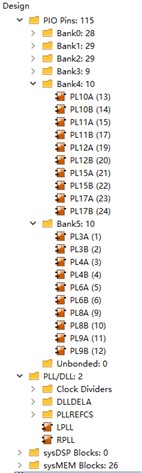

- FPGA XO2器件介紹:

- 器件料號: MachXO2:LCMXO2-7000HE-TQFP144

- Bank4 LVDS I/O:

- 使用 PLA10A/LVDS_D0+

- 使用 PLA10B/LVDS_D0-

- 使用 PLA11A/LVDS_D1+

- 使用 PLA11B/LVDS_D1-

- 使用 PLA12A/LVDS_D2+

- 使用 PLA12B/LVDS_D2-

- 使用 PLA15A/LVDS_D3+

- 使用 PLA15B/LVDS_D3-

- 使用 PLA10A/LVDS_clk+

- 使用 PLA17B/LVDS_clk-

- 使用 PLA3A /PWM

- 使用 PLA3B /MSL

- 使用 PLA4A /DPS

- 使用 PLA4B /FRC

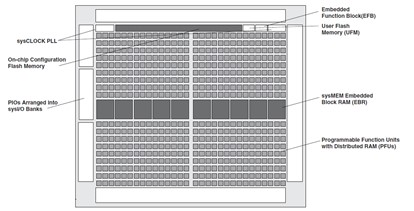

- FPGA內的資源:

- PLL:

- On chip OSC:

- EBR:

- PFU:

- LVDS I/O:

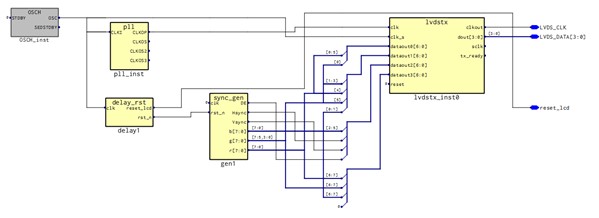

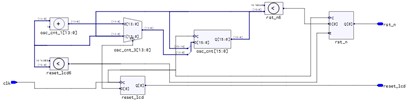

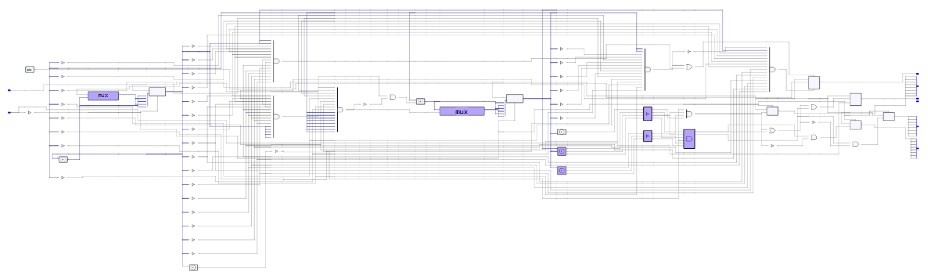

- 規劃FPGA邏輯模塊: (下圖為連接好的各模塊圖)

- 搭建 top module:

-

module top (

output wire reset_lcd,

//lvds pin

output wire LVDS_CLK,

output wire [3:0] LVDS_DATA );

這裡調用有用到的各IP模塊

. .(此處請自由發揮)

.

endmodule

-

- 搭建WPI 提供的IP:

-

delay_rst delay1(

.clk(osc_38),

.rst_n(rst_n),

.reset_lcd(reset_lcd)

);

-

sync_gen gen1(

.r(r),

.g(g),

.b(b),

.DE(DE),

.Vsync(Vsync),

.Hsync(Hsync),

.clk(clk),

.rst_n(rst_n)

)

-

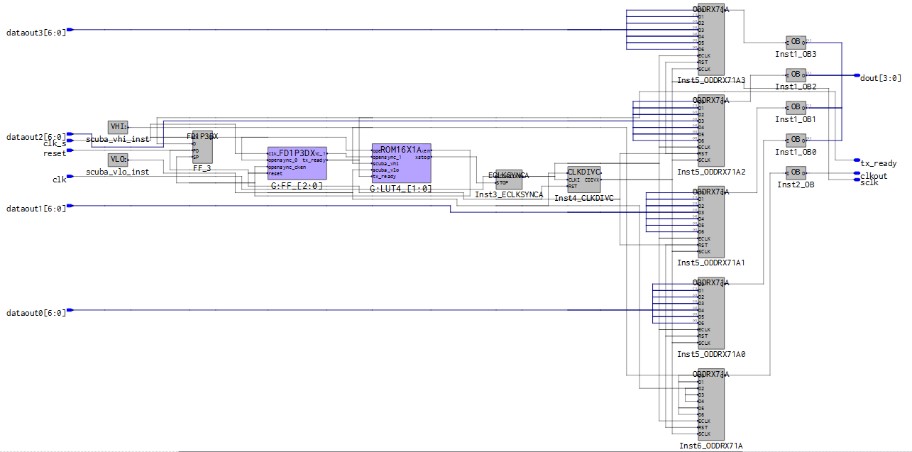

lvdstx lvdstx_inst0 (

.clk_s(osc_38 ),

.reset(1'b0 ),

.clk(pll_166 ),

.dataout0(tx0_a ),

.dataout1(tx0_b ),

.dataout2(tx0_c ),

.dataout3(tx0_d ),

.sclk( ),

.tx_ready( ),

//lvds pin

.clkout(LVDS_CLK ),

.dout(LVDS_DATA )

);

- 搭建原廠 提供的IP:

-

defparam OSCH_inst.NOM_FREQ = "38";

OSCH OSCH_inst(

.STDBY(1'b0),

.OSC(osc_38),

.SEDSTDBY()

); //synthesis syn_black_box

-

pll pll_inst (

.CLKI(osc_38 ),

.CLKOP(pll_166 ),

.CLKOS(pll_47 ),

.CLKOS2(pll_spi ),

.CLKOS3(pll_100 )

);

-

-

-

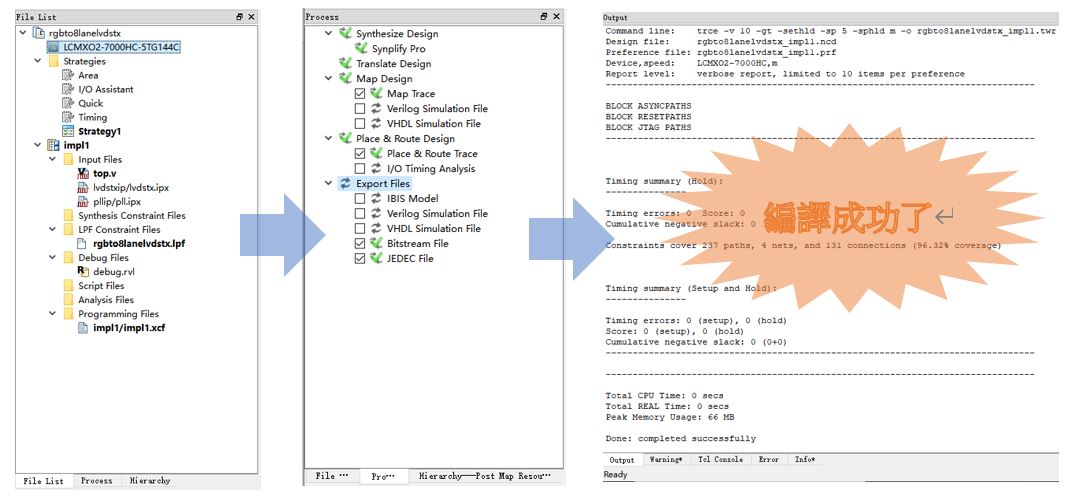

- 使用綜合佈局佈線工具:

-

- 下載燒錄程序到FPGA板子:

- 恭喜你!現在就可以看到顯示畫面囉!!

如果你想要再進階學習與使用本方案,趕快來連繫我吧!

大聯大控股世平集團

大聯大商貿有限公司

FPGA 系統開發 研發總監 鄭保夏 Jones Cheng

Office: 886-2-2788-5200臺北

86-21-23099388深圳#37048

Mobile:

(TW) +886 -930801444 台灣

(CN) +86-15801597488 北京

(CN) +86-15000264113 上海

E.mail: jones.cheng@wpi-group.com

WPI Group 世 平 集 團 A Member of WPG Holdings 大聯大控股

►場景應用圖

►展示板照片

►方案方塊圖

►可以用於電梯廂內顯示屏

►核心技術優勢

採用FPGA來驅動顯示屏TFT-LCD, 有著比MCU更高效能,及更高靈活度, 不論是 RGB888的並行接口或是LVDS的串型接口, 可以輕易定義封包內容,也能隨意地編解碼各家的顯示屏, 對於不同解析度和不同色深要求的應用場合,絕對是FPGA來做主控端再適合也不過了, 低的操作頻率,不發燙,省電等等優勢, 是你的方案首選

►方案規格

LVDS解析度支持 1920x1080p 以內, 禎率可以30fps 或60fps 支持自定義協議包, 支持通用LVDS標準協議包