最近,行業內玩家8英寸碳化矽量產如火如荼的進行中,安森美(onsemi)也計劃於今年晚些時候對8英寸碳化矽晶圓進行認證,並於2025年投入生產。而在柵極結構方面,平面結構和溝槽結構的爭論仍在繼續。兩者各有其優勢和劣勢,選擇哪種結構取決於具體的應用場景和需求,同時還要兼顧成本效益。前不久安森美推出的採用行業標準TO-247-4L封裝的1200V EliteSiC M3e平台,可以說是平面結構的登頂之作,再次刷新了高耗電應用的能效。

在PCIM Asia Shenzhen 2024上,安森美電源方案事業群資深產品專家Mrinal Das博士接受媒體專訪時表示,碳化矽對於電源創新應用的重要性不言而喻。入行30年,他親眼見證了碳化矽材料的發展歷程。針對當前碳化矽行業的一些熱點以及市場趨勢,他結合技術創新分享了自己的觀點,內容涵蓋IDM(垂直整合製造)模式、碳化矽平面與溝槽紛爭,以及FoM(品質因數)差異的權衡等。

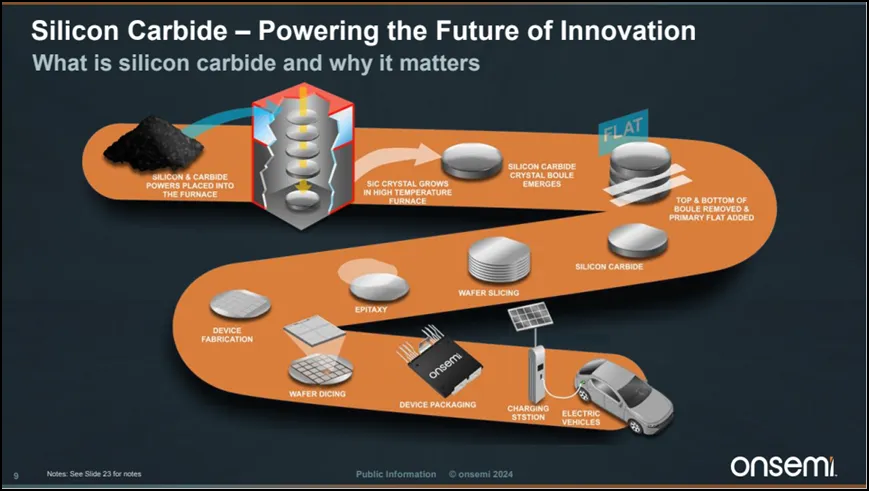

從矽碳化物的生產流程可以看出,從碳化矽粉末放入長晶爐,到最終產品電動汽車,整個過程包括多個步驟,如高溫晶體生長、碳化矽晶錠、晶體切割、晶體拋光、晶圓製備、封裝、測試和質量控制等。這些步驟確保了高質量的產品能夠滿足客戶的需求。

安森美的“智能電源”由SiC和Si功率驅動,在全球市場位居第二位。面向未來,公司設定了25%市場份額,在市場增長趨緩之時,安森美仍有望在 2024 年實現超過碳化矽市場 2 倍的增長。Mrinal Das博士表示,安森美充分考慮了供應鏈的穩定與靈活性。他明確指出:“安森美具備強大的供應鏈垂直整合能力,這意味著我們在很大程度上能夠自給自足地供應碳化矽襯底,滿足內部生產需求。”

他也坦言,作為一家負責任的企業,安森美深知風險管理與多元化供應策略的重要性。因此,儘管我們擁有強大的內部供應能力,但仍“留有餘量”,保留了與第三方供應商的合作渠道,以確保在市場需求發生未預見波動時,能夠迅速調整並滿足市場要求,降低整體生產風險。

其總體思路是,在碳化矽襯底供應上既依賴於自身強大的內部製造能力,也保持著與第三方供應商的靈活合作,以確保供應鏈的穩定性和韌性,為公司的長遠發展奠定堅實基礎。

Mrinal Das博士還深入解析了IDM模式在安森美運營中的優勢與挑戰,並闡述了安森美如何有效應對這些挑戰,以實現持續成功。

他指出,安森美在6英寸晶圓製造領域已建立起強大的產量和產能基礎,這是其市場優勢之一。更重要的是,安森美通過堅定的承諾和對市場需求的高度敏感性而與眾不同。基於市場需求的決策,可確保從6英寸到8英寸的過渡平穩且高效;選擇對客戶和自身最有價值的平台,有助於保持定價合理和供應穩定。這種保守而穩健的策略可以在市場中形成差異化競爭優勢。

此外,安森美之所以相對成功,還得益於採取的“棕地擴建”策略。在全球範圍內,安森美擁有多個晶圓廠,只通過少量投資即可轉化為碳化矽生產能力。這種靈活性使其能夠迅速響應市場需求,調整晶圓廠的使用分配。相比之下,沒有現有晶圓廠基礎的公司則需要進行大量的“綠地投資”,從頭開始建設生產線,這不僅成本高昂,而且時間周期長。

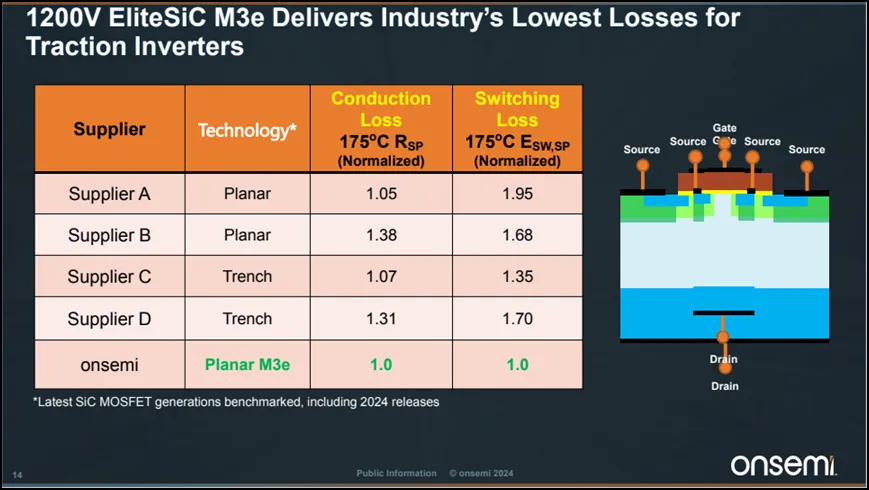

安森美新推出的EliteSiC M3e技術平台以其1200V、11mΩ MOSFET裸片為核心,憑藉行業領先的優值,在更高開關頻率與電壓下展現出卓越的性能,有效降低了功率轉換損耗。其獨特的平面拓撲經過現場驗證,以獨特方式降低了導通損耗和開關損耗,為電力電子行業樹立了質量與可靠性的新標杆。

與前幾代產品相比,M3e平台不僅將電氣化應用的傳導損耗減少了30%,開關損耗降低了50%,還以業界最低的具有短路能力的比導通電阻(RSP)賦能牽引逆變器市場。值得一提的是,M3e以更低的每千瓦成本提升了下一代電氣系統的性能和可靠性,同時減少了無源元件和熱管理成本,為用戶帶來前所未有的成本效益。

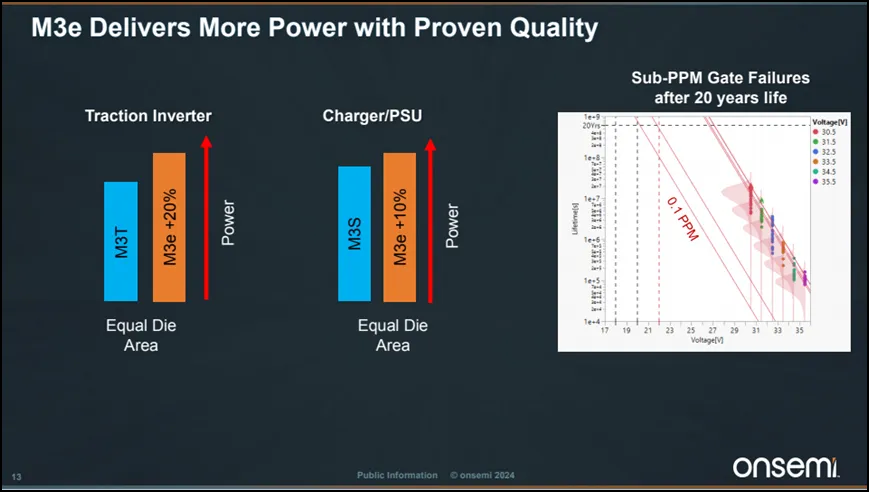

據介紹,採用安森美先進的分立和功率模塊封裝,1200V M3e裸片與之前的EliteSiC技術(M3T)相比,能夠提供更大的相電流,使同等尺寸主驅逆變器的輸出功率提升約20%,而在充電器和PSU(電腦電源)中,功率提高了10%。這意味著,在輸出功率不變的情況下,新設計所需的碳化矽材料可以相應減少,成本也更低,且能實現更小、更輕、更可靠的系統設計。

在質量保證方面,M3e 20年壽命後的柵極故障低於PPM,因此能夠讓客戶的產品在市場中脫穎而出。

Mrinal Das博士指出,在當前1200V碳化矽器件競爭激烈的市場環境下,許多廠商都在努力降低導通損耗和開關損耗。然而,對於最終用戶而言,他們更看重的是實際結果和性能提升。目前的方案,要麼是在固定的裸片數量的情況下去提升功率水平,要麼是在指定的功率水平之上來減少裸片數量。

M3e順應了市場趨勢,其核心目標是實現最佳的導通損耗和開關損耗。它通過裸片層面的優化,顯著降低了整體導通電阻,從而提高了系統開關效率,提升了整體性能表現。同時,通過採用更少裸片的並聯設計,簡化了系統結構,提高了系統的可用性和穩定性。

Mrinal Das博士介紹說,同樣是平面結構,M3e採用了明顯不同的結構,可以確保該平台的堅固性和穩定性,使其成為關鍵電氣化應用的首選技術。M3e業界最低的損耗主要歸功於其獨特的晶胞(Unit Cell)設計和內部創新。

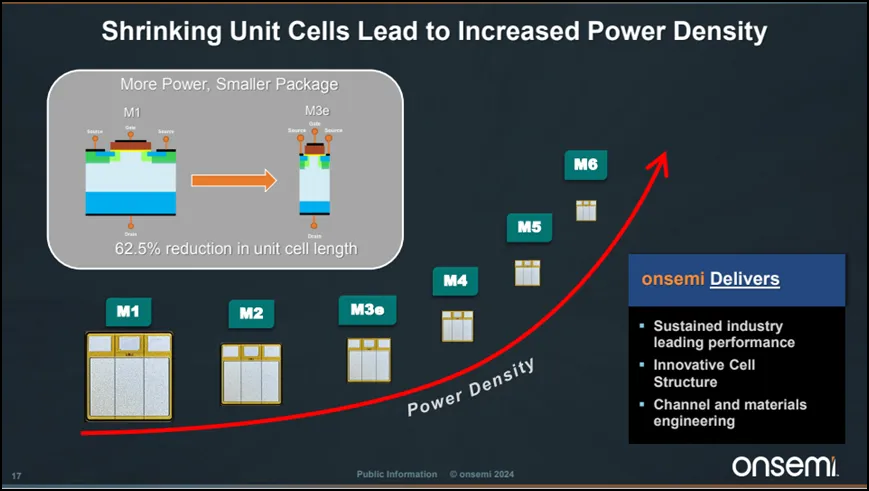

他解釋說,晶胞在功率MOSFET設計中非常關鍵,它是整個晶片上不斷複製的微型MOSFET的基本長度,包括兩個導電通道。事實上,儘可能縮小晶胞就可以增加功率密度。晶胞體積越小,每個晶片上可以放置的MOSFET就越多,而這些MOSFET是並聯的,所以整體的器件的電阻就會下降,晶胞本身的電阻也會下降。這兩種效應組合起來,就能夠進一步降低整個導通電阻,這是M3e導通損耗達到業界最低水平的主要原因。

從M1到M3e,晶胞的長度減少了62.5%,從而實現了更大的功率和更小的封裝,功率密度也在不斷提升。未來,這一過程將繼續演進,為市場提供行業領先的可持續性能、創新的晶胞結構以及渠道與材料工程。

另外,每個器件內部的開關損耗主要由電容決定,而主要的電容是柵極到漏極的電容。在M3e晶胞結構上進行的內部創新,使得柵極到漏極的電容更低,從而降低了整體的開關損耗。

那麼,安森美是怎麼把晶胞做到很小的?Mrinal Das博士回應道,安森美通過投資先進的晶圓廠工具和技術,不斷拓展現有生產設備的能力,確保能夠實現微型和微觀功能的精確製造。這一策略使得安森美能夠成功地將MOSFET的晶胞體積做得非常小,最大化利用了每一個晶片空間,提高了功率MOSFET的性能,並實現了大規模批量化生產。這種對技術創新的持續投入和追求,是安森美在行業中保持領先地位的關鍵因素之一。

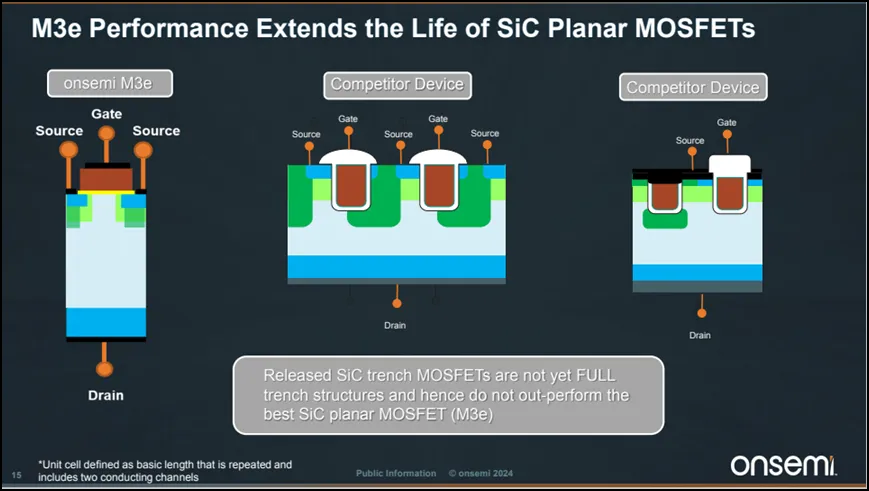

雖然溝槽拓撲的技術難度比較大,但一般來講它更能夠節省碳化矽材料,進而帶來成本效益。不過,安森美認為,目前溝槽的MOSFET還不是全溝槽結構,還難以體現溝槽結構的優勢。其中一些結構採用多個源極和柵極,有的則只有一個源極和一個柵極,並沒有達到最佳性能。

Mrinal Das博士對比了平面拓撲結構與溝槽拓撲結構,詳細闡述了安森美在MOSFET拓撲結構選擇上的考量。他指出,平面拓撲結構的主要優勢在於柵極氧化層的可靠性。柵極氧化層是平面拓撲MOSFET中最關鍵且最薄弱的環節。經過40年的研發和超過15年的市場驗證,平面拓撲結構在質量和可靠性方面已經得到了充分證明。

在討論碳化矽與矽材料在電力電子器件中的顯著差異時,他深入闡述了電場強度、柵極氧化物保護以及溝槽技術的複雜性。首先,相比傳統矽材料,碳化矽材料在電場強度上具有顯著優勢,其峰值電場強度可達到每厘米3MV(200-300kV/cm),是傳統矽材料的10倍以上。這一特性使得碳化矽在高壓、高功率應用中具有更高的效率和更小的體積,但同時也帶來了新的技術挑戰。

在溝槽器件設計中,柵極氧化層的位置至關重要。在平面結構中,柵極氧化物位於低電場區,相對安全。而在溝槽結構中,柵極氧化物暴露在高電場區,要求必須採取特殊措施來保護其免受高電場的影響,以防止柵極氧化層失效。這種保護在碳化矽器件中尤為困難,因為碳化矽的柵極保護機制與矽不同,無法直接借鑑矽材料的經驗。

此外,柵極氧化物在碳化矽溝槽技術中具有獨特性。與傳統的矽平面結構不同,碳化矽溝槽結構在側壁上交替堆疊矽和碳層,這種結構使得柵極氧化物表面引入了碳元素,從而改變了氧化物的性質。這種全新的氧化物不僅與平面結構中的氧化物不同,也與傳統矽功率器件中的氧化物大相徑庭。因此,溝槽技術在碳化矽器件中的推廣遇到了諸多延誤,因為所有的研究——包括製造性、可靠性和現場性能——都需要從頭開始,無法直接利用矽器件的成熟技術。

他強調,在碳化矽器件中採用溝槽技術所面臨的兩大技術挑戰:一是如何在高電場環境下有效保護柵極氧化層,因為柵極氧化層一旦暴露在磁場或電場中,很早就會出現失效的情況,其壽命會大大縮短。

二是如何應對溝槽結構中全新氧化物帶來的製造、可靠性和性能問題。這些挑戰要求在研發過程中投入更多的時間和精力,以積累必要的經驗,推動碳化矽溝槽技術的進一步發展。

對於M3e這樣的平面體結構MOSFET,Mrinal Das博士自信地表示,其性能甚至優於當前的溝槽器件。而溝槽結構在碳化矽面積利用方面並未展現出顯著優勢,尚未超越平面拓撲結構。

他預測,未來更多供應商可能還會選擇平面拓撲結構,除非溝槽結構在性能上能夠全面超越。“只有當溝槽技術的產品性能能夠全面超越平面拓撲結構時,我們才會考慮切換到溝槽技術。這表明我們在技術研發上持謹慎態度,注重產品的長期可靠性和性能表現。”他強調。

他還提到,市場上其他競爭對手的溝槽技術產品之所以性能不如M3e,主要原因是這些產品並未採用全溝槽技術。通過對採用的技術、導通損耗和開關損耗的對比,可以看到採用平面結構的M3e均優於其他供應商的產品,包括2024年發布的產品。

在他看來,M3e標誌著平面結構MOSFET性能的頂峰。如果要在未來的產品中實現更高的性能突破,的確要轉向溝槽技術,但前提是這種技術需要實現百分之百的溝槽利用率,以充分發揮碳化矽的潛力。

因此,安森美目前正全力以赴地應對新的挑戰,解決新的柵極氧化物的保護問題,同時實現百分之百的溝槽利用率。

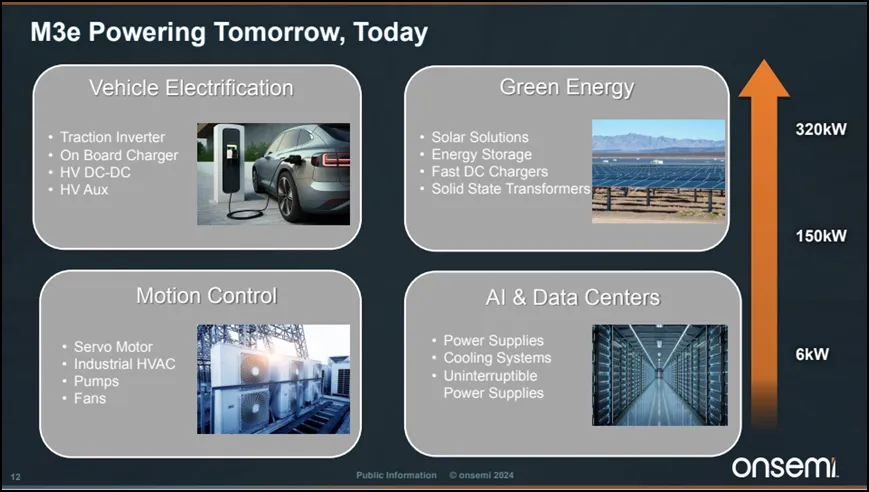

在探討碳化矽材料在不同應用場景下的性能優化時,Mrinal Das博士說,安森美憑藉其深厚的技術積累和敏銳的市場洞察,成功地在多個領域實現了卓越的性能表現。無論是硬開關、軟開關,還是高頻、低頻環境,安森美都能通過精準的技術調整和產品優化,確保每一款SiC MOSFET都能在各個使用場景中表現出色。

1200V EliteSiC M3e實現了牽引逆變器業界最低的損耗,安森美充分利用了碳化矽材料低開關損耗的特性,通過精細調控導通電阻(Rds)和柵極到漏極的電荷(Qgd),有效降低了器件在開關過程中的能量損失,使牽引逆變器的整體效率顯著提升。特別是在高功率密度和高效率要求的場合,這種優化顯得尤為重要。

車載充電器高頻應用場景則面臨更為複雜的挑戰,不僅需要處理高頻率的開關操作,還需要在硬開關和軟開關兩種模式下實現高效轉換。為此,安森美採用了創新的圖騰柱(Totem Pole)結構,並進一步優化了Rsp(導通損耗與硬開關損耗的比例)和柵極驅動器損耗。通過精確計算總柵極電荷,能夠準確預測並降低柵極驅動器電路中的能量損失,從而確保車載充電器在不同工作頻率下都能保持高效穩定的性能。

安森美深知不同應用場景下FoM的差異。在M3e等產品的研發過程中,安森美不僅關注單一的性能指標,更注重整體性能的最優化。通過跟蹤和參考Rds、Qgd、Rsp等關鍵參數,能夠確保新技術在開發過程中始終圍繞用戶需求和市場趨勢進行疊代和優化。這種以用戶需求為導向的技術開發策略,使安森美的SiC MOSFET在多個應用領域都展現出了卓越的性能和廣泛的應用前景。

Mrinal Das博士告訴記者,安森美也在利用摩爾定律思維加速碳化矽技術的疊代。其每一代碳化矽技術都會優化單元結構,在更小的面積上高效傳輸更大的電流,從而提高功率密度;同時結合自有的先進封裝技術,最大限度提升性能並減小封裝尺寸。這些計劃於2030年前推出的多款高性能新品,將進一步應對全球能源需求的激增。

他強調,碳化矽在功率密度與效率上的卓越表現,使其成為電動汽車、電網等關鍵領域的理想選擇,並預示其在未來新興應用場景中的廣闊潛力。

“只有憑藉深厚的功率半導體技術積累,不斷突破技術瓶頸,確保設計與製造的全面掌控,才能加速新一代碳化矽產品的市場化進程。”他相信,未來的下一代碳化矽技術在工業領域的採用和發展將會由這樣的公司來引領。

評論