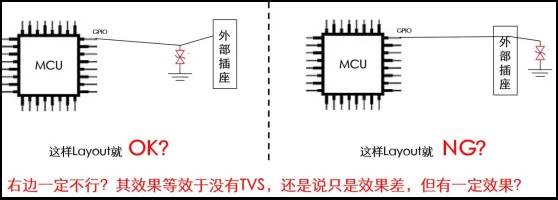

那如果受板子實際情況限制,必須這樣layout,是一定不行嗎?

有這個問題的原因,主要是因為兩點:

一是因為從原理圖上看來,二者並沒有區別,都是ESD元件接在同一個網路GPIO上面。既然沒有區別,那為什麼結果會有差異呢?對於新手來說,確實難以理解。

二是既然跟layout有關,那兩種不同的layout方式?到底是影響了什麼參數造成了這個差異呢?這些網上也沒有找到相關的較深入的文章。

問題的原因——走線電感

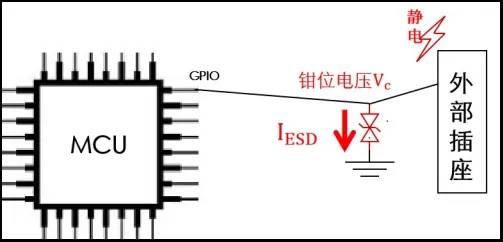

我們設想的是,放電時,靜電能量都從ESD元件這裡泄放掉,而不通過我們的晶片放電,這樣才能實現ESD元件保護晶片的目的。

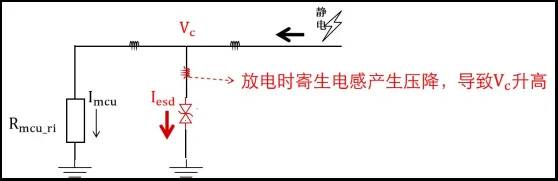

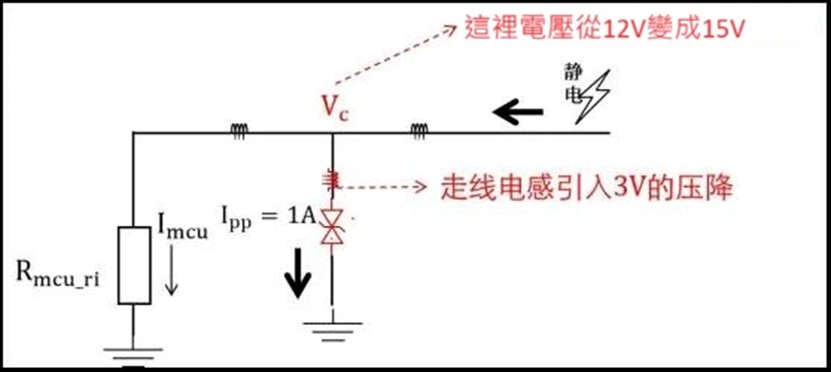

如上圖,理想情況下,如果ESD管的鉗位電壓足夠低,那麼靜電放電電流基本都從ESD元件進行泄放問題是,我們通常要通過PCB實現這個電路,PCB Layout走線也不是理想的,會有走線電感。

ESD放電時信號頻譜頻寬是幾十Mhz到500Mhz,是高頻的,而電感是頻率越高,阻抗越大。如果Layout引入寄生電感,ESD泄放的時候電流也會在電感上面形成壓降,導致晶片端殘壓升高,如果電壓高於了晶片的耐受電壓,那麼就會擊穿晶片,導致防護失敗。

上面說法還是籠統,下面我們拿資料說話。

走線電感的阻抗

很多人可能會認為走線電感,那不就是寄生電感嗎,聽起來就很小,不能直接忽略嗎?

能不能忽略自然就是看影響,只有沒影響的情況下才能忽略,那到底能不能忽略呢?

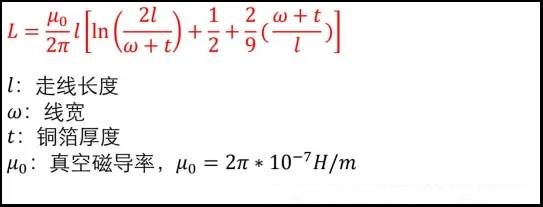

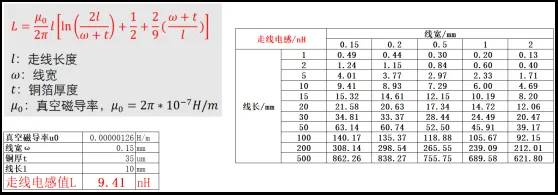

套用這個公式,可以得到走線長度1cm,寬度為6mil,銅厚為1oz的走線電感為9.41nH。

現在電感值已經有了,是9.41nH,我們根據公式ZL=jwL=2πfL,得到在50Mhz(ESD放電波形電流頻譜是幾十Mhz到500Mhz,在ESD釋放時能量主要集中在幾十Mhz這個頻率,所以取50Mhz)

時的阻抗ZL(50Mhz)=2*π*50Mhz*9.41nH≈3Ω。

電感走線阻抗已經知道了,那麼影響到底有多大呢?

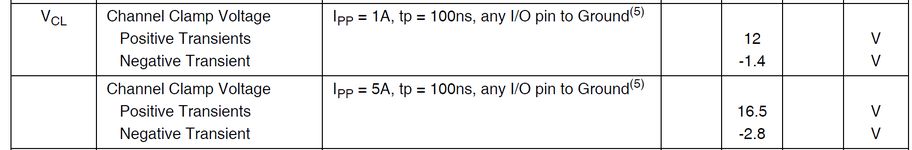

如果我們是理想Layout 的情況下(沒有寄生電感),那麼在ESD管泄放電流Ipp為1A的時候,鉗位電壓為12V。而如果現在Layout不好,引入了寄生電感,其50Mhz時,等效阻抗為3歐姆,如果電流依然是1A,那麼電感上面的壓降就是3V,這樣導致整體看起來,鉗位元電壓從12V提到到15V。

以上舉的是6mil,10mm的走線長度,這個走線長度已經是非常小的了,可以看到,它已經對我們的ESD性能造成了影響。 如果長度增加到10cm,從上表知道,走線電感就是140nh,50Mhz對應阻抗是ZL(50Mhz)=2*π*50Mhz*140nH≈43Ω,同樣的方法得到1A定流時的等效鉗位元電壓VC=55V,這是我們說這個ESD完全沒用應該是沒毛病的。

小結

本文主要是對於ESD元件的Layout要求的理解,主要從寄生電感的角度來說的,雖說文章有一些資料,但是整體還算是定性分析。實際情況是更為複雜的,比如說ESD管到MCU也有走線,也有寄生電感,這對ESD更為友好一點。還有就是如果寄生電感大了,ESD的泄放電流應該也會小一些,而上面的資料都是假設Ipp是1A時的情況。Q & A:

Q1:壓敏電阻也是用來防護因為電力供應系統的暫態電壓突波,所可能對電路之傷害,那它與TVS主要的差異為何?

Ans:兩者相對比,其結果是在施加1,000 次 8kV IEC 61000-4-2 ESD 脈衝條件下, TVS 元件的漏電流小於0.1 μA,而壓敏電阻在少於20 個ESD 脈衝下漏電流就會超過100 μA。由此可見,在重複ESD 應力作用下,TVS 仍能維持極高的性能,而壓敏電阻的性能會隨之下降,聚合物也面臨著跟壓敏電阻類似的問題。

Q2:TVS與Zener Diode的差別為何?

Q3:TVS二極體單向的及雙向的差異為何?

Ans:單向的TVS二極體在順向操作時類似整流器,但在其設計允許承受很大的峰值電流,雙向的TVS二極體可以視為是二個極性相反的雪崩二極體相串聯,再和要保護的電路並聯。雖然在電路中會標示為二個二極體,不過實際元件是將二個二極體封裝在同一個包裝中。

Q4:TVS若是採用SCR電路設計,為何會不適用在某些Type-C接口應用?

Ans:在Type-C接口的防護電路中,如果TVS選型不恰當,使用SCR電路設計的TVS應用在VBUS端或者CC Pin線路時,更容易發生Latch-up風險,當然信號線同樣也會發生此風險。主要原因是ESD、Surge等瞬態突波耦合到接口線路時,外部突波電壓高於TVS的擊穿電壓時,TVS就會導通開啟。若因為選型不當,TVS開啟後Snap-back電壓(Vsb or Vhold),低於電源正常工作電壓Vbus或者Data信號電壓的最大值VMAX,即使外部突波干擾消失,TVS也會一直保持導通狀態,此時電流大量增加,電源電壓將被拉低或者正常信號傳輸將被干擾,嚴重時TVS燒毀短路,造成器件或者整個電路被EOS損壞。

Q5:AOS TVS優勢何在?

Ans:AOS TVS二極體,其特點為反應速度快,體積小,脈衝功率較大,超低鉗位電壓等特性,對於超高速訊號需求推出,也有推行一系列相關的產品。

Q6 : 可以推薦那幾個料號及應用?

Ans: AOZ8S201BMS-05 / AOZ8S312BD4-03 / AOZ8S303BLS-24 / AOZ8S315BLS-05

AOZ8S201BMS-05 : Low operating voltage: 3.3V, 5V. Low capacitance: 0.075pF.

USB4, Thunderbolt 4, PCI Express.

AOZ8S312BD4-03 : Super-low capacitance (<0.1pF).

Super/high-speed interfaces such as Thunderbolt 4.0/3.0, USB4.0/3.2/3.1/3.0, HDMI2.1/2.0.

AOZ8S303BLS-24 : Low operating voltage: 24V, Low capacitance: 0.2pF.

USB3.2, Thunderbolt, PCI Express

AOZ8S315BLS-05 : Low operating voltage: 3.3V, 5V.

USB4, Thunderbolt 4, PCI Express.

參考來源