原文標題: Practical Aspects and Body Diode Robustness of a 1200 V SiC Trench MOSFET

原文作者: Thomas Basler

原文發表在 PCIM Europe 2018, 5 – 7 June 2018, Nuremberg

Si IGBT和SiC溝槽MOSFET之間有許多電氣及物理方面的差異,Practical Aspects and Body Diode Robustness of a 1200V SiC Trench MOSFET 這篇文章主要分析了在SiC MOSFET中比較明顯的短溝道效應、Vth滯回效應、短路特性以及體二極體的魯棒性。 直接翻譯不免晦澀難懂,不如加入自己的理解,重新梳理一遍,希望能給大家帶來更多有價值的信息。 今天我們著重看下第一部分——短溝道效應。

Si IGBT/MOSFET與SiC MOSFET,儘管襯底材料不一樣,但是形成柵極氧化層的材料卻是一樣的——都是SiO2。 Si C-SiO2界面缺陷大於Si-Si O2界面,界面缺陷會降低反型層溝道遷移率,進而提高溝道電阻。 對於SiC MOSFET,儘管人們花了很多精力來提高溝道遷移率,但其遷移率仍然遠遠低於矽的IGBT/MOSFET。

(更詳細的解釋請參考:SiC MOSFET真的有必要使用溝槽柵嗎? )

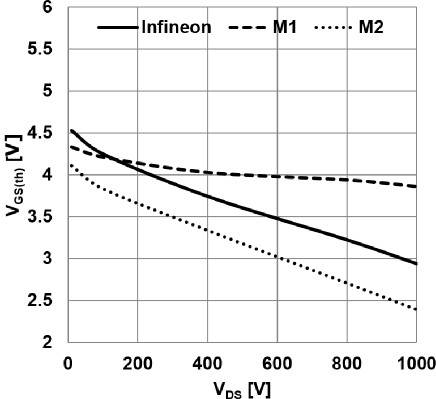

因此,商用SiC MOSFET會設計成具有相對較短的反型層溝道,以儘量減少其溝道電阻。 對於1200V的SiC MOSFET來說,溝道電阻對整個RDS,on的貢獻最大,這與高壓Si MOSFET完全不同。 此外,對於溝槽MOSFET,由於SiC漂移區厚度較低,基極摻雜較高,因此溝道區附近的電場強度(特別是在開關期間)比Si MOSFET高。 為了保護柵極氧化物,必須有一個屏蔽結構,這在所有現代SiC MOSFET概念中都可以找到。 與矽器件相比,上述效應導致了更明顯的漏極勢壘降低效應(DIBL-或短溝道效應)。 DIBL效應的原理大家可以在百度搜到,這裡就不再贅述了。 DIBL效應造成的明顯的現象是——隨著漏極-源極電壓VDS的增加,柵-源極閾值電壓VGS(th)會隨之降低,見圖1。

Fig.1:不同製造商1200V SiC MOSFET的VGS(th)曲線,Infineon-溝槽,M1-溝槽,M2-平面

DIBL效應和柵極電荷

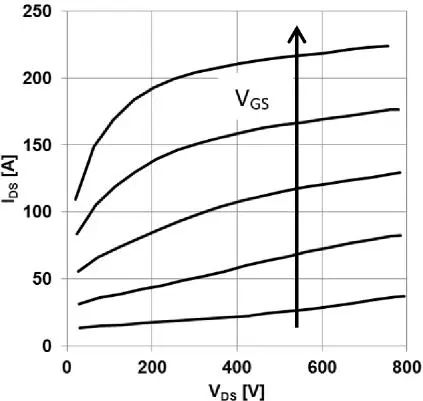

由於上述的DIBL效應,與IGBT相比,SiC MOSFET的輸出特性看起來有所不同。 在相同VGS條件下,器件的飽和電流隨VDS上升而上升。 見圖2。

圖2:45mΩ、1200V SiC溝槽MOSFET在25°C時不同VGS下的輸出特性曲線。 該特性是在短路狀態下,通過非常短的脈衝測量的,並在考慮到測量期間溫度上升的情況。

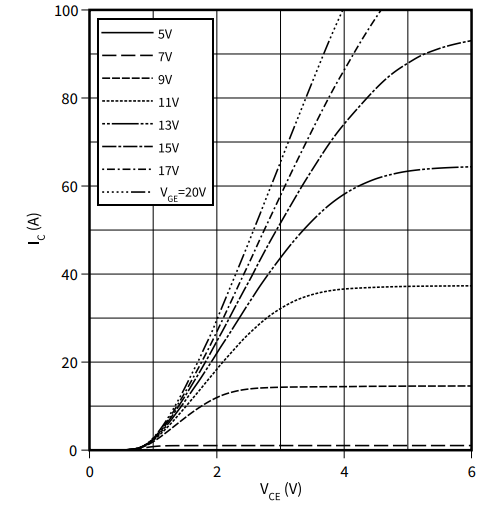

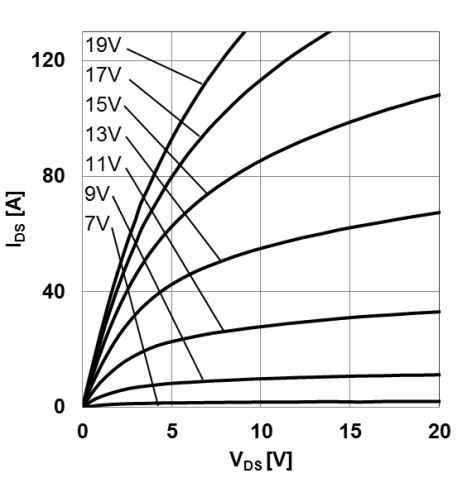

矽IGBT通常使用更長的反型溝道,溝道電阻對靜態損耗來說是次要的。 阻斷狀態下的電場較小,因此,DIBL效應較低,飽和電流不會隨DS電壓上升而變化太大。 下圖(左)是IGBT的輸出特性曲線,可以看到,線性區和飽和區之間的分界點很清楚,曲線進入飽和狀態之後的部分非常平坦,而SiC MOSFET的分界點則沒那麼明顯,即使進入飽和狀態,電流曲線仍有一定斜率的上升。

典型的IGBT輸出特性曲線(左)與SiC MOSFET輸出特性曲線(右)

由於SiC-MOS器件的VGS(th)隨著漏極電壓的增加而減少,飽和電流ID,sat上升得更明顯,原因可參見以下公式,可以看到,飽和電流與過驅動電壓(VGS-V GSth)的平方成正比。

其中k為一個常數

W-溝道寬度,μn-電子遷移率,Cox–柵氧化層電容,L–溝道長度

對系統進行短路保護設計必須考慮DIBL的影響。 例如,我們需要知道直流母線電壓下的退飽和電流水平。 在器件設計中,可以通過更有效的p-屏蔽結構和更長的溝道來減少DIBL效應。 然而,這兩個參數也可能導致更高的RDS,on。

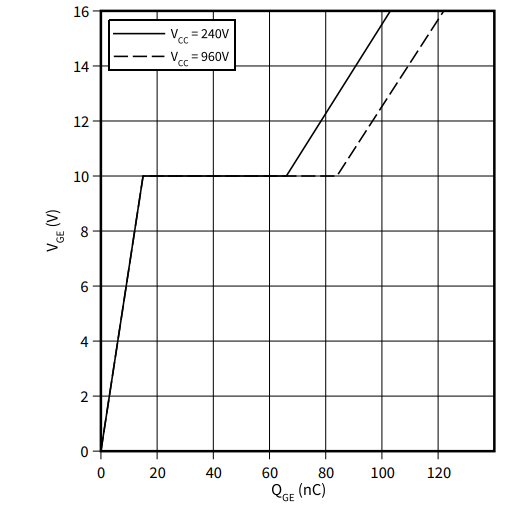

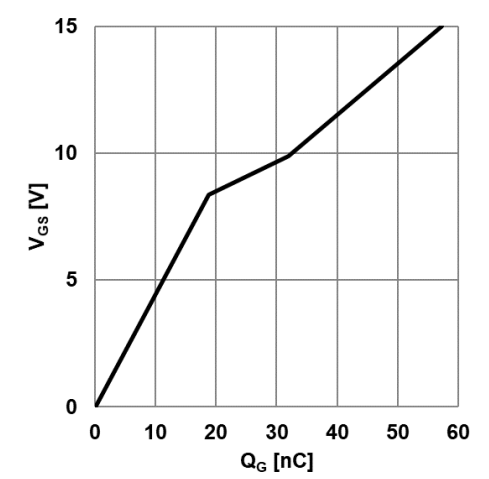

DIBL的第二個效應可以通過圖3中的柵極電荷曲線來觀察。 VDS變化期間的VGS是一個斜坡,而IGBT的典型柵極電荷曲線,這時是一個恆定的VGS值。

柵極電荷曲線對比:IGBT與SiC MOSFET

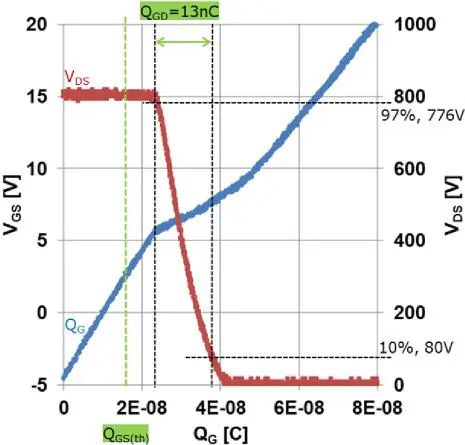

因此,在計算重要參數QGD時,使用斜坡時間段是不正確的。 更合適的方法是將VDS波形與QG特性疊加在同一張圖上,並如圖3所示設置取值範圍(取10%VDS~97%VDS)。

圖3:英飛凌45mΩ/1200V晶片的柵極電荷特性(藍色),在800V、20A、25°C、VGS-5V→15V的情況下,開通時測量,利用VDS(紅色)波形提取QGD

這其實是在對測得的小信號電容CGD進行積分。

上述方法可得45mΩ器件QGD為13nC。 從圖3中還可以提取使VGS達到閾值水平所需的電荷(QGS,th,約18nC),可以發現QGD/QGS,th之比小於1。 這有助於抑制寄生導通,即在VDS快速變化的情況下,通過CGD給柵極充電的電荷量,小於使柵極電壓VGS抬升至閾值VGSth的電荷量。

總結一下,商業化的SiC MOSFET普遍採用短溝道設計,用來降低導通電阻,這使得DIBL(漏致勢壘降低效應)比較明顯。 SiC MOSFET中的DIBL效應首先表現在飽和電流隨VDS上升而上升,其次表現在柵極電荷曲線中的米勒平台段呈斜線。 從圖中計算得出SiC的QGD需要將VDS與柵極電荷曲線疊加在一起,通過限定邊界條件的方式得出。

參考閱讀

文章來源:英飛凌工業半導體

請掃描二維碼關注英飛凌工業半導體微信

評論